- English

- Español

- Português

- русский

- Français

- 日本語

- Deutsch

- tiếng Việt

- Italiano

- Nederlands

- ภาษาไทย

- Polski

- 한국어

- Svenska

- magyar

- Malay

- বাংলা ভাষার

- Dansk

- Suomi

- हिन्दी

- Pilipino

- Türkçe

- Gaeilge

- العربية

- Indonesia

- Norsk

- تمل

- český

- ελληνικά

- український

- Javanese

- فارسی

- தமிழ்

- తెలుగు

- नेपाली

- Burmese

- български

- ລາວ

- Latine

- Қазақша

- Euskal

- Azərbaycan

- Slovenský jazyk

- Македонски

- Lietuvos

- Eesti Keel

- Română

- Slovenski

- मराठी

- Srpski језик

ກະດານ MCU ARM STM32

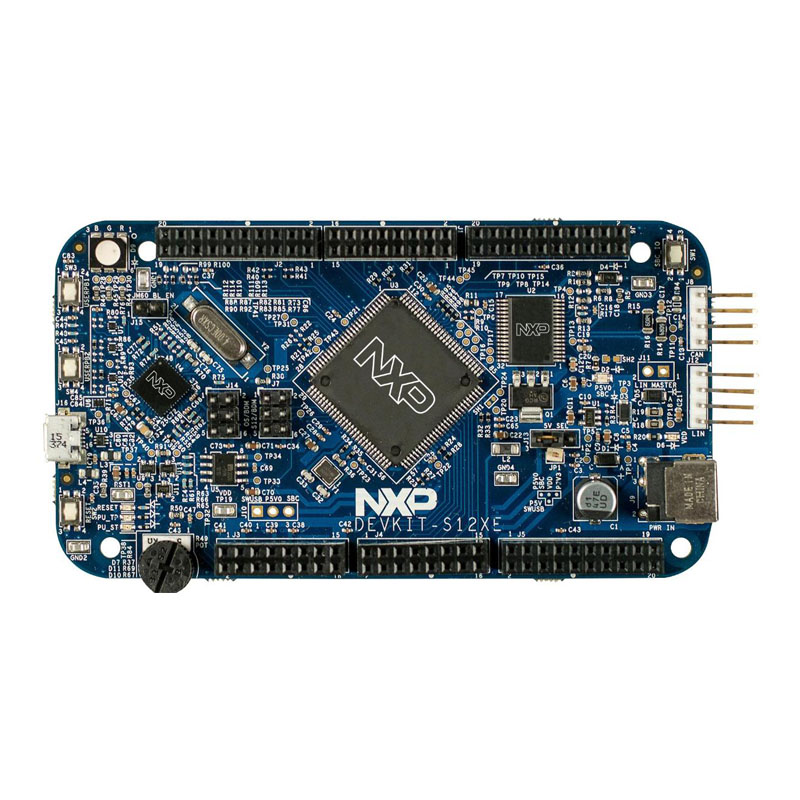

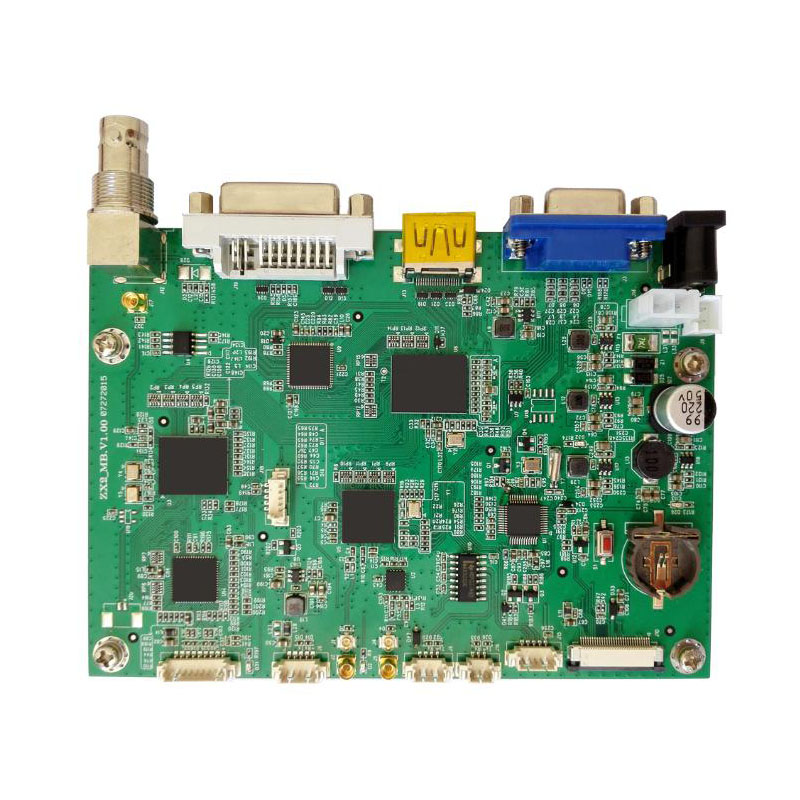

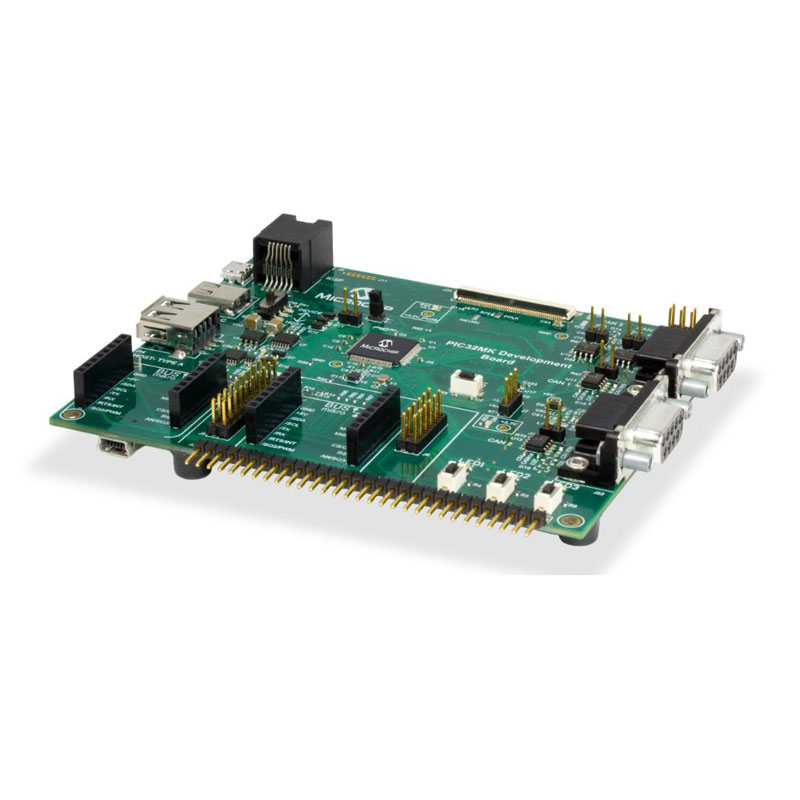

Ningbo Hi-tech Easy Choice Technology Co., Ltd ເປັນບໍລິສັດເຕັກໂນໂລຢີສູງທີ່ມີການເຄື່ອນໄຫວໃນການອອກແບບ, ການພັດທະນາແລະການຜະລິດກະດານ ARM STM32 MCU. ຊື່ສຽງຂອງບໍລິສັດຂອງພວກເຮົາແມ່ນສ້າງຂຶ້ນໃນສິນເຊື່ອທີ່ດີແລະການສະຫນອງການບໍລິການພິເສດ, ເຊິ່ງໄດ້ສົ່ງຜົນໃຫ້ມີການຮ່ວມມືໃນໄລຍະຍາວກັບບໍລິສັດທີ່ສໍາຄັນ, ອົງການຂອງລັດຖະບານ, ແລະຊຸມຊົນຜູ້ໃຊ້ທີ່ກວ້າງຂວາງ. ພວກເຮົາມີຄວາມຊ່ຽວຊານໃນການພັດທະນາກະດານຄວບຄຸມເອເລັກໂຕຣນິກອັດສະລິຍະ, ການອອກແບບຜະລິດຕະພັນຄວບຄຸມກົນຈັກແລະໄຟຟ້າ, ການພັດທະນາ microcomputer ຊິບດຽວ, ການອອກແບບວົງຈອນ, ແລະການທົດສອບຫລັງການຜະລິດ. ພວກເຮົາອາດຈະອອກແບບວົງຈອນການຄວບຄຸມເພື່ອຕອບສະຫນອງຄວາມຕ້ອງການຂອງທ່ານ, ເຮັດໃຫ້ການປະຕິບັດຫນ້າທີ່ຜະລິດຕະພັນທີ່ຕັ້ງໄວ້ຂອງທ່ານ, ບໍ່ວ່າທ່ານຈະສະຫນອງຂໍ້ກໍານົດການທໍາງານທີ່ຊັດເຈນຫຼືພຽງແຕ່ຄວາມຄິດ.

ສົ່ງສອບຖາມ

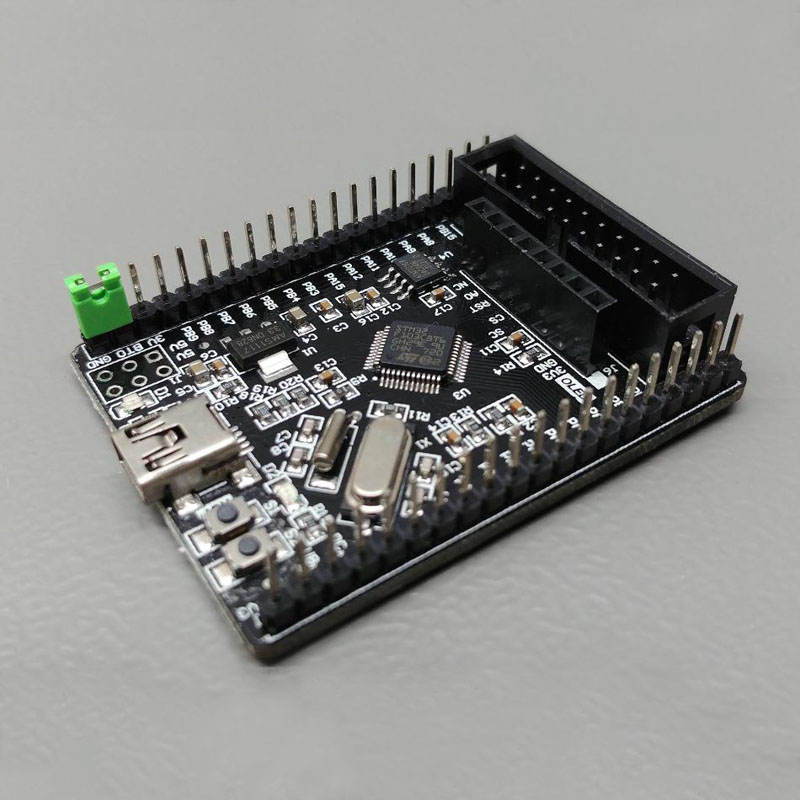

ການພັດທະນາກະດານຄວບຄຸມຜະລິດຕະພັນອຸດສາຫະກໍາ YCTECH ລວມມີການອອກແບບຊອບແວກະດານຄວບຄຸມອຸດສາຫະກໍາ, ການຍົກລະດັບຊອບແວ, ການອອກແບບແຜນວາດແຜນວາດ, ການອອກແບບ PCB, ການຜະລິດ PCB ແລະການປຸງແຕ່ງ PCBA ທີ່ຕັ້ງຢູ່ໃນຝັ່ງຕາເວັນອອກຂອງປະເທດຈີນ. ບໍລິສັດຂອງພວກເຮົາອອກແບບ, ພັດທະນາ ແລະຜະລິດກະດານ ARM STM32 MCU. Core: ARM32-bit Cortex-M3 CPU, ຄວາມຖີ່ຂອງການເຮັດວຽກສູງສຸດແມ່ນ 72MHz, 1.25DMIPS/MHz. ຄູນຮອບດຽວ ແລະແບ່ງຮາດແວ.

ຫນ່ວຍຄວາມຈໍາ: On-chip ປະສົມປະສານ 32-512KB ຫນ່ວຍຄວາມຈໍາ Flash. 6-64KB ຂອງຫນ່ວຍຄວາມຈໍາ SRAM.

ໂມງ, ປັບແລະການຄຸ້ມຄອງພະລັງງານ: ການສະຫນອງພະລັງງານ 2.0-3.6V ແລະແຮງດັນໄຟຟ້າສໍາລັບການໂຕ້ຕອບ I / O. ຣີເຊັດການເປີດເຄື່ອງໃໝ່ (POR), ຣີເຊັດການເປີດເຄື່ອງໃໝ່ (PDR), ແລະເຄື່ອງກວດຈັບແຮງດັນທີ່ຕັ້ງໂປຣແກຣມໄດ້ (PVD). 4-16MHz crystal oscillator. Built-in 8MHz RC oscillator circuit ປັບກ່ອນໂຮງງານ. ພາຍໃນ 40 kHz RC oscillator circuit. PLL ສໍາລັບໂມງ CPU. 32kHz ໄປເຊຍກັນກັບການປັບທຽບສໍາລັບ RTC.

ການໃຊ້ພະລັງງານຕໍ່າ: 3 ໂໝດການໃຊ້ພະລັງງານຕໍ່າ: ນອນ, ຢຸດ, ໂໝດສະແຕນບາຍ. VBAT ເພື່ອພະລັງງານ RTC ແລະທະບຽນສໍາຮອງ.

ໂຫມດດີບັກ: ດີບັກ serial (SWD) ແລະການໂຕ້ຕອບ JTAG.

DMA: ຕົວຄວບຄຸມ DMA 12 ຊ່ອງ. ອຸປະກອນຕໍ່ພ່ວງທີ່ຮອງຮັບ: ເຄື່ອງຈັບເວລາ, ADC, DAC, SPI, IIC ແລະ UART.

ເຄື່ອງແປງ A/D ລະດັບ 12-ບິດ us-level (16 ຊ່ອງ): ໄລຍະການວັດແທກ A/D: 0-3.6V. ຕົວຢ່າງຄູ່ແລະຄວາມສາມາດຖື. ເຊັນເຊີອຸນຫະພູມແມ່ນປະສົມປະສານຢູ່ໃນຊິບ.

2-channel 12-bit converter D/A: STM32F103xC, STM32F103xD, STM32F103xE ສະເພາະ.

ເຖິງ 112 ພອດ I/O ໄວ: ຂຶ້ນກັບຕົວແບບ, ມີ 26, 37, 51, 80, ແລະ 112 ພອດ I/O, ເຊິ່ງທັງໝົດສາມາດສ້າງແຜນທີ່ເປັນ 16 ແວກເຕີລົບກວນພາຍນອກ. ທັງໝົດແຕ່ການປ້ອນຂໍ້ມູນແບບອະນາລັອກສາມາດຍອມຮັບໄດ້ເຖິງ 5V.

ສູງສຸດ 11 ເຄື່ອງຈັບເວລາ: 4 ເຄື່ອງຈັບເວລາ 16-bit, ແຕ່ລະຕົວມີ 4 IC/OC/PWM ຫຼືຕົວນັບກຳມະຈອນ. ສອງ 16-bit 6-channel timers ການຄວບຄຸມຂັ້ນສູງ: ສູງສຸດ 6 ຊ່ອງສາມາດໄດ້ຮັບການນໍາໃຊ້ສໍາລັບຜົນຜະລິດ PWM. 2 ຕົວຈັບເວລາເຝົ້າລະວັງ (ຕົວເຝົ້າຍາມແບບເອກະລາດ ແລະ ປ່ອງຢ້ຽມເຝົ້າລະວັງ). ເຄື່ອງຈັບເວລາ Systick: 24-bit down counter. ສອງເຄື່ອງຈັບເວລາພື້ນຖານ 16-bit ຖືກໃຊ້ເພື່ອຂັບ DAC.

ສູງສຸດ 13 ການໂຕ້ຕອບການສື່ສານ: 2 ການໂຕ້ຕອບ IIC (SMBus/PMBus). 5 ການໂຕ້ຕອບ USART (ອິນເຕີເຟດ ISO7816, LIN, IrDA ເຂົ້າກັນໄດ້, ການຄວບຄຸມດີບັກ). 3 ອິນເຕີເຟດ SPI (18 Mbit/s), ສອງອັນນັ້ນຖືກຄູນດ້ວຍ IIS. ການໂຕ້ຕອບ CAN (2.0B). ການໂຕ້ຕອບຄວາມໄວເຕັມ USB 2.0. ການໂຕ້ຕອບ SDIO.

ຊຸດ ECOPACK: STM32F103xx ຊຸດ microcontrollers ຮັບຊຸດ ECOPACK.

ຜົນກະທົບຂອງລະບົບ

1. ARM Cortex-M3 core ປະສົມປະສານກັບ Flash ຝັງແລະຫນ່ວຍຄວາມຈໍາ SRAM. ເມື່ອປຽບທຽບກັບອຸປະກອນ 8/16-bit, ARM Cortex-M3 32-bit RISC processor ໃຫ້ປະສິດທິພາບລະຫັດທີ່ສູງຂຶ້ນ. ໄມໂຄຄອນຄວບຄຸມ STM32F103xx ມີຫຼັກ ARM ທີ່ຝັງໄວ້, ດັ່ງນັ້ນພວກມັນເຂົ້າກັນໄດ້ກັບທຸກເຄື່ອງມື ແລະຊອບແວ ARM.

2. Embedded Flash memory ແລະ RAM memory: Built-in up to 512KB embedded Flash, ເຊິ່ງສາມາດໃຊ້ເພື່ອເກັບໂປຣແກມ ແລະ ຂໍ້ມູນ. ສູງສຸດ 64KB ຂອງ SRAM ຝັງຕົວສາມາດອ່ານແລະຂຽນດ້ວຍຄວາມໄວຂອງໂມງ CPU (ບໍ່ມີສະຖານະລໍຖ້າ).

3. ໜ່ວຍຄວາມຈຳສະຖິດຕົວປ່ຽນແປງ (FSMC): FSMC ຖືກຝັງຢູ່ໃນ STM32F103xC, STM32F103xD, STM32F103xE, ມີ 4 ຊິບເລືອກ, ແລະຮອງຮັບສີ່ໂຫມດຄື: Flash, RAM, PSRAM, NOR ແລະ NAND. 3 ສາຍຂັດຈັງຫວະ FSMC ແມ່ນເຊື່ອມຕໍ່ກັບ NVIC ຫຼັງຈາກ OR. ບໍ່ມີການອ່ານ / ຂຽນ FIFO, ຍົກເວັ້ນ PCCARD, ລະຫັດຖືກປະຕິບັດຈາກຫນ່ວຍຄວາມຈໍາພາຍນອກ, Boot ບໍ່ໄດ້ຮັບການສະຫນັບສະຫນູນ, ແລະຄວາມຖີ່ຂອງເປົ້າຫມາຍແມ່ນເທົ່າກັບ SYSCLK/2, ດັ່ງນັ້ນເມື່ອໂມງລະບົບແມ່ນ 72MHz, ການເຂົ້າເຖິງພາຍນອກແມ່ນປະຕິບັດຢູ່ທີ່ 36MHz.

4. Nested Vectored Interrupt Controller (NVIC): ມັນສາມາດຈັດການ 43 ຊ່ອງລົບກວນທີ່ສາມາດປິດບັງໄດ້ (ບໍ່ລວມ 16 ເສັ້ນຂັດຈັງຫວະຂອງ Cortex-M3), ສະຫນອງ 16 ບູລິມະສິດຂັດຂວາງ. NVIC ປະສົມປະສານຢ່າງແຫນ້ນຫນາບັນລຸຄວາມລ່າຊ້າຂອງການປະມວນຜົນຕ່ໍາ, ໂອນໂດຍກົງທີ່ຢູ່ຕາຕະລາງ vector entry ລົບກວນໄປຫາ kernel, ເຊື່ອມຕໍ່ NVIC kernel ຢ່າງແຫນ້ນຫນາ, ອະນຸຍາດໃຫ້ຂັດຂວາງການປຸງແຕ່ງລ່ວງຫນ້າ, ຈັດການການຂັດຂວາງທີ່ມີບູລິມະສິດສູງກວ່າທີ່ມາຮອດຕໍ່ມາ, ແລະສະຫນັບສະຫນູນ tail Chain, ຊ່ວຍປະຢັດອັດຕະໂນມັດ. ສະຖານະຂອງໂປເຊດເຊີ, ແລະການເຂົ້າຂັດຂວາງຈະຖືກຟື້ນຟູໂດຍອັດຕະໂນມັດເມື່ອການຂັດຂວາງອອກຈາກ, ໂດຍບໍ່ມີການແຊກແຊງຄໍາແນະນໍາ.

5. External interrupt/event controller (EXTI): The external interrupt/event controller consists of 19 edge detector lines for generating interrupt/event requests. Each line can be individually configured to select the trigger event (rising edge, falling edge, or both) and can be individually masked. There is a pending register to maintain the status of interrupt requests. EXTI is able to detect when a pulse on the external line is longer than the period of the internal APB2 clock. Up to 112 GPIOs are connected to 16 external interrupt lines.

6. Clock and start: It is still necessary to select the system clock when starting, but the internal 8MHz crystal oscillator is selected as the CPU clock when resetting. An external 4-16MHz clock can be selected and will be monitored for success. During this time, the controller is disabled and software interrupt management is subsequently disabled. At the same time, interrupt management of the PLL clock is fully available if required (eg in case of failure of an indirectly used crystal oscillator). Multiple pre-comparators can be used to configure the AHB frequency, including high-speed APB (PB2) and low-speed APB (APB1). The highest frequency of high-speed APB is 72MHz, and the highest frequency of low-speed APB is 36MHz.

7. ໂຫມດ Boot: ໃນຕອນເລີ່ມຕົ້ນ, Boot pin ຖືກນໍາໃຊ້ເພື່ອເລືອກຫນຶ່ງໃນສາມທາງເລືອກ Boot: ນໍາເຂົ້າຈາກຜູ້ໃຊ້ Flash, ນໍາເຂົ້າຈາກຫນ່ວຍຄວາມຈໍາຂອງລະບົບ, ແລະນໍາເຂົ້າຈາກ SRAM. ໂປລແກລມນໍາເຂົ້າ Boot ແມ່ນຢູ່ໃນຫນ່ວຍຄວາມຈໍາຂອງລະບົບແລະຖືກນໍາໃຊ້ເພື່ອ reprogram ຫນ່ວຍຄວາມຈໍາ Flash ຜ່ານ USART1.

8. ລະບົບການສະຫນອງພະລັງງານ: VDD, ລະດັບແຮງດັນແມ່ນ 2.0V-3.6V, ການສະຫນອງພະລັງງານພາຍນອກແມ່ນສະຫນອງໃຫ້ໂດຍຜ່ານ VDD pin, ເຊິ່ງຖືກນໍາໃຊ້ສໍາລັບ I / O ແລະເຄື່ອງຄວບຄຸມແຮງດັນພາຍໃນ. VSSA ແລະ VDDA, ລະດັບແຮງດັນແມ່ນ 2.0-3.6V, ແຮງດັນໄຟຟ້າອະນາລັອກພາຍນອກເຂົ້າສໍາລັບ ADC, ໂມດູນ reset, RC ແລະ PLL, ພາຍໃນຂອບເຂດຂອງ VDD (ADC ແມ່ນຈໍາກັດ 2.4V), VSSA ແລະ VDDA ຕ້ອງເຊື່ອມຕໍ່ກັບ VSS ຕາມຄວາມເຫມາະສົມ. ແລະ VDD. VBAT, ລະດັບແຮງດັນແມ່ນ 1.8-3.6V, ເມື່ອ VDD ບໍ່ຖືກຕ້ອງ, ມັນສະຫນອງພະລັງງານສໍາລັບ RTC, ພາຍນອກ 32KHz crystal oscillator ແລະທະບຽນສໍາຮອງ (ຮັບຮູ້ໂດຍການປ່ຽນພະລັງງານ).

9. ການຈັດການພະລັງງານ: ອຸປະກອນມີວົງຈອນການຣີເຊັດການເປີດເຄື່ອງໃໝ່ (POR) ແລະ ວົງຈອນປິດເປີດຄືນໃໝ່ (PDR). ວົງຈອນນີ້ມີປະສິດຕິຜົນສະເຫມີເພື່ອຮັບປະກັນວ່າບາງການດໍາເນີນງານທີ່ຈໍາເປັນໄດ້ຖືກປະຕິບັດໃນເວລາທີ່ເລີ່ມຕົ້ນຈາກ 2V ຫຼືຫຼຸດລົງເຖິງ 2V. ເມື່ອ VDD ຕ່ຳກວ່າຂອບເຂດຈຳກັດສະເພາະ VPOR/PDR, ອຸປະກອນຍັງສາມາດຢູ່ໃນໂໝດຣີເຊັດໄດ້ໂດຍບໍ່ຕ້ອງມີວົງຈອນຣີເຊັດພາຍນອກ. ອຸປະກອນນີ້ມີເຄື່ອງກວດຈັບແຮງດັນຂອງໂຄງການຝັງ (PVD). PVD ຖືກນໍາໃຊ້ເພື່ອກວດຫາ VDD ແລະປຽບທຽບມັນກັບຂອບເຂດຈໍາກັດ VPVD. ການຂັດຂວາງແມ່ນຖືກສ້າງຂຶ້ນເມື່ອ VDD ຕ່ໍາກວ່າ VPVD ຫຼື VDD ແມ່ນໃຫຍ່ກວ່າ VPVD. ການຂັດຂວາງການບໍລິການປົກກະຕິສາມາດສ້າງຂໍ້ຄວາມເຕືອນຫຼືວາງ MCU ຢູ່ໃນສະພາບທີ່ປອດໄພ. PVD ຖືກເປີດໃຊ້ໂດຍຊອບແວ.

10. ລະບຽບການແຮງດັນ: ເຄື່ອງຄວບຄຸມແຮງດັນມີ 3 ໂຫມດປະຕິບັດການ: ຕົ້ນຕໍ (MR), ການບໍລິໂພກພະລັງງານຕ່ໍາ (LPR) ແລະພະລັງງານລົງ. MR ຖືກນໍາໃຊ້ໃນໂຫມດລະບຽບການ (ຮູບແບບການແລ່ນ) ໃນຄວາມຫມາຍພື້ນເມືອງ, LPR ແມ່ນໃຊ້ໃນໂຫມດຢຸດ, ແລະພະລັງງານລົງແມ່ນໃຊ້ໃນໂຫມດສະແຕນບາຍ: ແຮງດັນໄຟຟ້າແຮງດັນໄຟຟ້າແຮງດັນສູງ, ວົງຈອນຫຼັກແມ່ນພະລັງງານລົງ, ລວມທັງ. ການບໍລິໂພກສູນ (ເນື້ອໃນຂອງການລົງທະບຽນແລະ SRAM ຈະບໍ່ສູນເສຍ).

11. ໂຫມດການບໍລິໂພກພະລັງງານຕ່ໍາ: STM32F103xx ສະຫນັບສະຫນູນ 3 ໂຫມດການໃຊ້ພະລັງງານຕ່ໍາ, ເພື່ອບັນລຸຄວາມສົມດຸນທີ່ດີທີ່ສຸດລະຫວ່າງການໃຊ້ພະລັງງານຕ່ໍາ, ເວລາເລີ່ມຕົ້ນສັ້ນແລະແຫຼ່ງປຸກທີ່ມີຢູ່. ໂໝດນອນ: ພຽງແຕ່ CPU ຢຸດເຮັດວຽກ, ອຸປະກອນຕໍ່ພ່ວງທັງ ໝົດ ສືບຕໍ່ແລ່ນ, ປຸກ CPU ເມື່ອມີການລົບກວນ / ເຫດການເກີດຂື້ນ; ໂໝດຢຸດ: ອະນຸຍາດໃຫ້ຮັກສາເນື້ອໃນຂອງ SRAM ແລະລົງທະບຽນດ້ວຍການໃຊ້ພະລັງງານໜ້ອຍທີ່ສຸດ. ໂມງໃນພາກພື້ນ 1.8V ຖືກຢຸດທັງຫມົດ, PLL, HSI ແລະ HSE RC oscillators ຖືກປິດໃຊ້ງານ, ແລະເຄື່ອງຄວບຄຸມແຮງດັນແມ່ນຖືກຈັດໃສ່ໃນໂຫມດພະລັງງານປົກກະຕິຫຼືຕ່ໍາ. ອຸປະກອນສາມາດຖືກປຸກຈາກໂຫມດຢຸດໂດຍຜ່ານສາຍລົບກວນພາຍນອກ. ແຫຼ່ງ interrupt ພາຍນອກສາມາດເປັນຫນຶ່ງໃນ 16 ສາຍ interrupt ພາຍນອກ, ຜົນຜະລິດ PVD ຫຼື TRC ເຕືອນ. ໂຫມດສະແຕນບາຍ: ໃນການຕິດຕາມການໃຊ້ພະລັງງານຫນ້ອຍທີ່ສຸດ, ຕົວຄວບຄຸມແຮງດັນພາຍໃນຖືກປິດ, ດັ່ງນັ້ນພື້ນທີ່ 1.8V ຖືກປິດ. PLL, HSI ແລະ HSE RC oscillators ຍັງຖືກປິດໃຊ້ງານ. ຫຼັງຈາກເຂົ້າສູ່ໂຫມດສະແຕນບາຍ, ນອກເຫນືອຈາກການລົງທະບຽນສໍາຮອງຂໍ້ມູນແລະວົງຈອນສະແຕນບາຍ, ເນື້ອໃນຂອງ SRAM ແລະທະບຽນຍັງສູນເສຍ. ອຸປະກອນຈະອອກຈາກໂໝດສະແຕນບາຍເມື່ອຣີເຊັດພາຍນອກ ( PIN NRST), ຣີເຊັດ IWDG, ຂອບຂຶ້ນເທິງ WKUP pin ຫຼື ການເຕືອນ TRC ເກີດຂຶ້ນ. ເມື່ອເຂົ້າສູ່ໂໝດຢຸດ ຫຼືໂໝດສະແຕນບາຍ, TRC, IWDG ແລະແຫຼ່ງໂມງທີ່ກ່ຽວຂ້ອງຈະບໍ່ຖືກຢຸດ.